改进的ESD保护技巧

- 编辑:admin -改进的ESD保护技巧

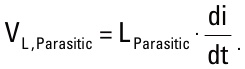

1简介,使用低于130 nm的先进技术开发了最新电子产品中使用的许多芯片,从LCD电视到手机。这些技术对于高于3.3V的CC电压非常不稳定,因此静电放电脉冲可能会对此类设备产生灾难性影响。此外,ESD保护要求“船上”或“座椅上”已减少到500V。这远低于8 kV站点的典型要求。本文解释了如果所选的ESD保护设备未通过系统的ESD测试,则表设计人员可以使用表设计人员可以使用的各种技术达到设计的水平。餐桌设计人员不仅需要保护外部静电放电,而且还要考虑到一小部分几何芯片的脆弱性,以保证足够坚固且耐用。如上一个文档中所述,将ESD设备放在受保护的数据线或I/O中的ESD设备中PIN不能保证芯片组本身在系统中的测试中通过8 kV。通常,ESD设备本身没有提供足够的保护,这可能会导致早期的芯片组故障。本文列出了一些设计师提供的指南,以提供参考,以改善船上的ESD保护。 2设备的位置和设计对于确保ESD保护器可以最大化其有效性很重要。为此,设计师更了解板上几个寄生虫的电感器的影响。特殊注意力是电感器,因为在PCB线中仅通过8 kV ESD冲击(即30 A)产生30 V峰值电压。注意:该讨论假设所有ESD威胁都必须通过图1中的端口输入该系统。必须考虑LGND,LIC和LPOR。图1显示了其位置。尽管LESD和LGND具有增加夹具(或VIC)的效果,但LIC和LPOR电压对设计师有益。首先,让我们看看这两个有害电感器。 3 WITH LESD和LGND,板的设计不允许将ESD设备直接放置在PCB电路上。原因有所不同,但最终将静电放电元件与受保护数据线1 cm的静电元件迅速变成几十伏。 GND巴士也可以这样说。在某些设计中,ESD设备的GND必须穿过多个孔,并穿过弯路才能到达GND平面。除了流经ESD设备的ESD电流产生的电压外,这两个电感器还会产生电压峰(即IIAK * RDYNAGIC)。以下简化的示例iLustera在Vís中的LESD和LGND的效果:在设置示例之前,应注意,典型的PCB制造过程可以为典型的微丝图迹线提供大约3 nh/cm(假设特定的宽度,厚度,厚度,恒定的介电常数)。鉴于您所拥有的,假设具有8 kV ESD脉冲的ESD设备和T中的1Ω动态电阻他的榜样。此外,让我们看看两种不同的设计:设计A和设计B。让我们看一下设计B:Lesd = lgnd = 1.5 nh(每个0.5厘米)和Lesd = lgnd = 3.0 nh(每个1.0厘米)。因此,通过将痕量(即Lesd,LGND)的量从0.5 cm增加到1 cm,可以将VIC增加75%。图2显示了B设计和与每个组件相关的电压。图2与设计相关的电压示例4 LIC的ESD设备的许多数据表,通常说明该设备与ESD入口点尽可能接近。目的是使LSP与LEC关系尽可能小(即LICPOR)。 LPOR的电感不一定会影响ESD的一般性能,但是LIC的电感肯定是正确的。 LIC冲击的非线性通过提供大型电压下降“朝向集成电路”,从而吸收了ESD脉冲的初始最大功率。随着电感器的减小(即ESD设备接近集成电路),电压下降继续降低,直到创建额外的好处。因此,对于设计师,要利用PCB电路的寄生特性,LiCport的关系就可以尽可能小。图3显示了引用的电压下降。图3集成电路电压cabzando lic and lport。这是提高ESD一般性能的直接方法。但是,无论以前的关系如何,有些设计过早地失败了。换句话说,LIC的值不能为最大ESD电流提供足够的减震器。当5个缓冲区电阻时,上述技术不足以为特定电路板设计提供最大的ESD保护。原因是“芯片中的ESD结构”中的电流太高,这会在缩短GND或VCC时I/S损害。图4显示了ESD设备和受保护的集成电路真正共享电流脉冲电流负载。这有助于更清楚地解释问题。该图(较小的迹线电感)显示出正静电放电脉冲。在这里,保护器负责大多数电流,但本质上是一个具有集成电路的电阻电压。 (注意:该图表明,集成电路在两个导轨中都有二极管夹具,但是芯片保护装置将是其他静电放电结构,例如晶状体。其目的是表明芯片中的ESD结构与ESD设备具有一定的平行电阻)。如图4所示,集成电路中的导轨二极管负责指导残留电流或“离开” VCC(通常通过派生电容器返回GND)。很难确定电路集成的ESD保护的等效电阻是什么,但绝对比船上的ESD设备高得多。对于前对于芯片保护器(RCHIP),外部ESD保护器的电阻为1Ω,外部ESD保护器的RDINA为1Ω,并且集成电路的最大电流如下:减少抗抗电路的最大电流,抗抗性系列添加了集成电阻,如下图5。显然,电阻值高于10Ω,以进一步降低泄漏电流。最大阻力通常取决于应用程序的特定情况。同样重要的是要记住,在使用该技术具有一些高速度应用程序(例如HDMI或USB 3.0)时,应格外小心。 ruffer电阻会干扰线阻抗,并导致信号的衰减超出两个标准合规规范,但是仔细设计板可以补偿副作用。但是,董事会的设计师必须将该技术维护在其工具箱中,并在ESD堤防(ESD)l关节或系统的要求低于要求。 6今天的结论,最后的芯片组更容易受到ESD渡轮的影响。多亏了小规模的几何技术,这些集成的电路需要强大的外部ESD解决方案来抵抗系统中的ESD测试。本文介绍了董事会设计师可以使用的四个策略或步骤来优化其ESD解决方案。 ●减少“存根”寄生虫或Lesd的长度。 ●减少旅行号,以减少GND和/或LGND线的长度。 ●LIC A LIC以尽可能多地进行特定设计。 ●如果以前的1-3个元素还不够,请在ESD设备和集成电路之间使用缓冲区电阻。所有这些实践旨在降低集成电路中的电压,并限制芯片中ESD结构应处理的电流。遵循这些简单的规则,联合设计人员可以获得超过这些行业的更强大的ESD解决方案。

1简介,使用低于130 nm的先进技术开发了最新电子产品中使用的许多芯片,从LCD电视到手机。这些技术对于高于3.3V的CC电压非常不稳定,因此静电放电脉冲可能会对此类设备产生灾难性影响。此外,ESD保护要求“船上”或“座椅上”已减少到500V。这远低于8 kV站点的典型要求。本文解释了如果所选的ESD保护设备未通过系统的ESD测试,则表设计人员可以使用表设计人员可以使用的各种技术达到设计的水平。餐桌设计人员不仅需要保护外部静电放电,而且还要考虑到一小部分几何芯片的脆弱性,以保证足够坚固且耐用。如上一个文档中所述,将ESD设备放在受保护的数据线或I/O中的ESD设备中PIN不能保证芯片组本身在系统中的测试中通过8 kV。通常,ESD设备本身没有提供足够的保护,这可能会导致早期的芯片组故障。本文列出了一些设计师提供的指南,以提供参考,以改善船上的ESD保护。 2设备的位置和设计对于确保ESD保护器可以最大化其有效性很重要。为此,设计师更了解板上几个寄生虫的电感器的影响。特殊注意力是电感器,因为在PCB线中仅通过8 kV ESD冲击(即30 A)产生30 V峰值电压。注意:该讨论假设所有ESD威胁都必须通过图1中的端口输入该系统。必须考虑LGND,LIC和LPOR。图1显示了其位置。尽管LESD和LGND具有增加夹具(或VIC)的效果,但LIC和LPOR电压对设计师有益。首先,让我们看看这两个有害电感器。 3 WITH LESD和LGND,板的设计不允许将ESD设备直接放置在PCB电路上。原因有所不同,但最终将静电放电元件与受保护数据线1 cm的静电元件迅速变成几十伏。 GND巴士也可以这样说。在某些设计中,ESD设备的GND必须穿过多个孔,并穿过弯路才能到达GND平面。除了流经ESD设备的ESD电流产生的电压外,这两个电感器还会产生电压峰(即IIAK * RDYNAGIC)。以下简化的示例iLustera在Vís中的LESD和LGND的效果:在设置示例之前,应注意,典型的PCB制造过程可以为典型的微丝图迹线提供大约3 nh/cm(假设特定的宽度,厚度,厚度,恒定的介电常数)。鉴于您所拥有的,假设具有8 kV ESD脉冲的ESD设备和T中的1Ω动态电阻他的榜样。此外,让我们看看两种不同的设计:设计A和设计B。让我们看一下设计B:Lesd = lgnd = 1.5 nh(每个0.5厘米)和Lesd = lgnd = 3.0 nh(每个1.0厘米)。因此,通过将痕量(即Lesd,LGND)的量从0.5 cm增加到1 cm,可以将VIC增加75%。图2显示了B设计和与每个组件相关的电压。图2与设计相关的电压示例4 LIC的ESD设备的许多数据表,通常说明该设备与ESD入口点尽可能接近。目的是使LSP与LEC关系尽可能小(即LICPOR)。 LPOR的电感不一定会影响ESD的一般性能,但是LIC的电感肯定是正确的。 LIC冲击的非线性通过提供大型电压下降“朝向集成电路”,从而吸收了ESD脉冲的初始最大功率。随着电感器的减小(即ESD设备接近集成电路),电压下降继续降低,直到创建额外的好处。因此,对于设计师,要利用PCB电路的寄生特性,LiCport的关系就可以尽可能小。图3显示了引用的电压下降。图3集成电路电压cabzando lic and lport。这是提高ESD一般性能的直接方法。但是,无论以前的关系如何,有些设计过早地失败了。换句话说,LIC的值不能为最大ESD电流提供足够的减震器。当5个缓冲区电阻时,上述技术不足以为特定电路板设计提供最大的ESD保护。原因是“芯片中的ESD结构”中的电流太高,这会在缩短GND或VCC时I/S损害。图4显示了ESD设备和受保护的集成电路真正共享电流脉冲电流负载。这有助于更清楚地解释问题。该图(较小的迹线电感)显示出正静电放电脉冲。在这里,保护器负责大多数电流,但本质上是一个具有集成电路的电阻电压。 (注意:该图表明,集成电路在两个导轨中都有二极管夹具,但是芯片保护装置将是其他静电放电结构,例如晶状体。其目的是表明芯片中的ESD结构与ESD设备具有一定的平行电阻)。如图4所示,集成电路中的导轨二极管负责指导残留电流或“离开” VCC(通常通过派生电容器返回GND)。很难确定电路集成的ESD保护的等效电阻是什么,但绝对比船上的ESD设备高得多。对于前对于芯片保护器(RCHIP),外部ESD保护器的电阻为1Ω,外部ESD保护器的RDINA为1Ω,并且集成电路的最大电流如下:减少抗抗电路的最大电流,抗抗性系列添加了集成电阻,如下图5。显然,电阻值高于10Ω,以进一步降低泄漏电流。最大阻力通常取决于应用程序的特定情况。同样重要的是要记住,在使用该技术具有一些高速度应用程序(例如HDMI或USB 3.0)时,应格外小心。 ruffer电阻会干扰线阻抗,并导致信号的衰减超出两个标准合规规范,但是仔细设计板可以补偿副作用。但是,董事会的设计师必须将该技术维护在其工具箱中,并在ESD堤防(ESD)l关节或系统的要求低于要求。 6今天的结论,最后的芯片组更容易受到ESD渡轮的影响。多亏了小规模的几何技术,这些集成的电路需要强大的外部ESD解决方案来抵抗系统中的ESD测试。本文介绍了董事会设计师可以使用的四个策略或步骤来优化其ESD解决方案。 ●减少“存根”寄生虫或Lesd的长度。 ●减少旅行号,以减少GND和/或LGND线的长度。 ●LIC A LIC以尽可能多地进行特定设计。 ●如果以前的1-3个元素还不够,请在ESD设备和集成电路之间使用缓冲区电阻。所有这些实践旨在降低集成电路中的电压,并限制芯片中ESD结构应处理的电流。遵循这些简单的规则,联合设计人员可以获得超过这些行业的更强大的ESD解决方案。